LVDS差分晶振600mV至1200mV輸出擺幅介紹

來源:http://www.11ed.cn 作者:金洛鑫電子 2019年09月21

在現今的電子和智能系統里,已經逐漸開始采用LVDS,LV-PECL輸出差分晶振為產品的性能加持,LVDS是比較常用的輸出邏輯之一,LVDS的在百度上的定義是: 低電壓差分信號,是一種低功耗,低誤碼率,低串擾和低輻射的差分信號技術,這種傳輸技術可以達到155Mbps以上,LVDS技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接.本文的主要目的,就是為大家介紹并講解,差分振蕩器LVDS輸出的600mV至1200mV輸出擺幅.

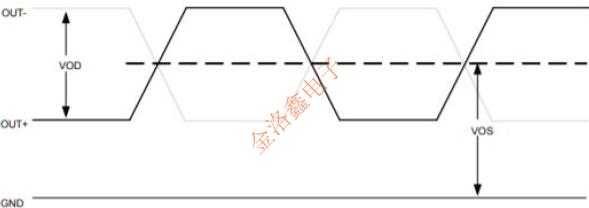

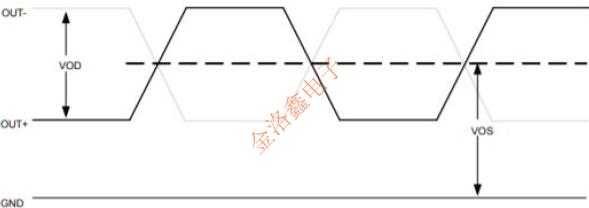

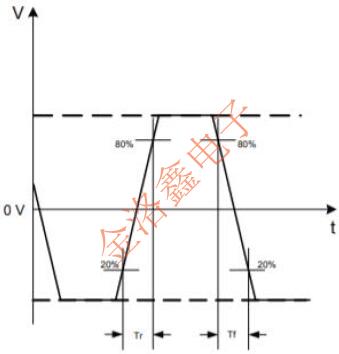

如下圖1.1所示,具有600mV至1200mV的差分擺幅的參考時鐘輸出已成為光模塊的常見要求,并由芯片組輸入要求驅動.差分擺幅的定義為OUT+減去OUT-,這就是差分接收器將如何處理波形.例如,在第2頁的圖1.2中所示,在單端模式下測量每個差分輸出時,相對于示波器觀察,OUT+減去OUT-會有效地使波形幅度加倍.由于不同的差分輸出格式對差分波形擺幅的定義可能不同,因此與芯片組供應商(最好是波形圖)確認確切的要求非常重要.

圖1.2.差分輸出單端視圖

LVDS輸出操作原理:

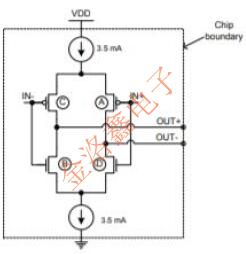

LVDS是一款高速數字接口,適合許多需要低功耗和高抗噪能力的應用.LVDS輸出使用低電壓擺幅差分信號以高速傳輸數據.下一頁顯示了LVDS驅動器的輸出結構,包括3.5毫安標稱電流源,通過開關網絡連接到差分輸出,有時也稱為“高”開關.輸出通常連接到100ω差分傳輸線,接收器輸入端端接一個100ω電阻.電阻值與傳輸線的阻抗匹配,并為信號提供電流路徑. 該驅動器包括將共模電壓設置為標稱值為1.2V的電路,與VDD無關.因此,無需在外部將驅動器偏置到任何特定電壓.同樣,LVDS輸出可以連接到任何LVDS輸入,而無需擔心振蕩器的實際電源電壓.信號切換是通過四個標有A,B,C和D的晶體管完成的.由于接收器的阻抗通常很高,因此來自驅動器的幾乎所有電流都流經標準的100差分端接電阻器,導致電壓差為350接收器輸入之間的mV.在圖2.1中,當信號IN為低電平時,晶體管A和B導通;電流流過

當信號IN為高電平時,晶體管C和D導通;當信號IN為高電平時,晶體管C和D導通.電流流過晶體管C和100電阻,然后流過晶體管D,在接收器兩端產生-350mV電壓.從接收器的角度來看,流過端接電阻器的電流的方向確定是否記錄了正或負差分電壓.正的差分電壓表示邏輯高電平,而負的差分電壓表示邏輯低電平.

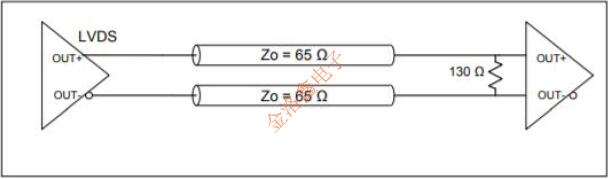

將LVDS差分擺幅調整為600mV至1200mV

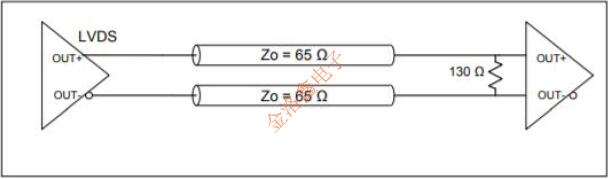

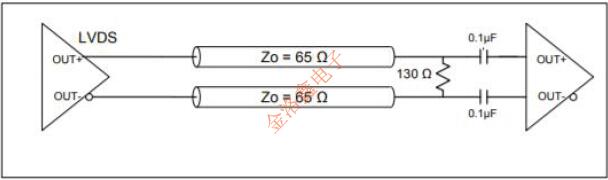

具有LVDS輸出和標準100終端的SiTime可編程振蕩器的差分輸出擺幅典型值為700mV,最小至最大窗口為500mV至900mV.要將LVDS的差分擺幅調整到600mV至1200mV的范圍,SiTime建議使用130Ω的端接電阻,如下圖3.0所示.它將典型的輸出擺幅值移至910mV,最小至最大范圍移至650mV至1170mV.為了使傳輸線和終端電阻完全匹配,建議將線阻抗增加到65Ω.

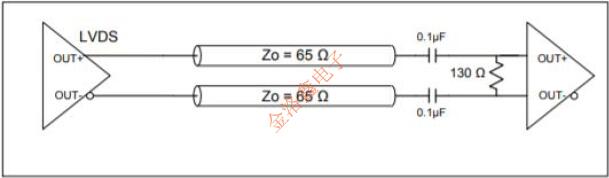

圖3.1.負載下的LVDS單AC端接

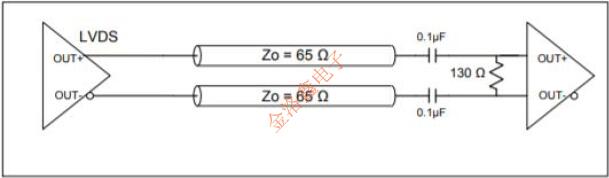

圖3.2.負載下的LVDS單AC端接

如果LVDS驅動器和接收器使用不同的共模電壓工作,則建議使用AC端接.電容器用于阻止來自驅動器的直流電流路徑,因此接收器必須實現自己的輸入偏置電路.交流耦合終端電路如圖3.1和圖3.2所示.如這些端接圖所示,交流耦合電容器可以放置在晶振負載端接電阻之前或之后.

如下圖1.1所示,具有600mV至1200mV的差分擺幅的參考時鐘輸出已成為光模塊的常見要求,并由芯片組輸入要求驅動.差分擺幅的定義為OUT+減去OUT-,這就是差分接收器將如何處理波形.例如,在第2頁的圖1.2中所示,在單端模式下測量每個差分輸出時,相對于示波器觀察,OUT+減去OUT-會有效地使波形幅度加倍.由于不同的差分輸出格式對差分波形擺幅的定義可能不同,因此與芯片組供應商(最好是波形圖)確認確切的要求非常重要.

圖1.2.差分輸出單端視圖

LVDS是一款高速數字接口,適合許多需要低功耗和高抗噪能力的應用.LVDS輸出使用低電壓擺幅差分信號以高速傳輸數據.下一頁顯示了LVDS驅動器的輸出結構,包括3.5毫安標稱電流源,通過開關網絡連接到差分輸出,有時也稱為“高”開關.輸出通常連接到100ω差分傳輸線,接收器輸入端端接一個100ω電阻.電阻值與傳輸線的阻抗匹配,并為信號提供電流路徑. 該驅動器包括將共模電壓設置為標稱值為1.2V的電路,與VDD無關.因此,無需在外部將驅動器偏置到任何特定電壓.同樣,LVDS輸出可以連接到任何LVDS輸入,而無需擔心振蕩器的實際電源電壓.信號切換是通過四個標有A,B,C和D的晶體管完成的.由于接收器的阻抗通常很高,因此來自驅動器的幾乎所有電流都流經標準的100差分端接電阻器,導致電壓差為350接收器輸入之間的mV.在圖2.1中,當信號IN為低電平時,晶體管A和B導通;電流流過

當信號IN為高電平時,晶體管C和D導通;當信號IN為高電平時,晶體管C和D導通.電流流過晶體管C和100電阻,然后流過晶體管D,在接收器兩端產生-350mV電壓.從接收器的角度來看,流過端接電阻器的電流的方向確定是否記錄了正或負差分電壓.正的差分電壓表示邏輯高電平,而負的差分電壓表示邏輯低電平.

將LVDS差分擺幅調整為600mV至1200mV

具有LVDS輸出和標準100終端的SiTime可編程振蕩器的差分輸出擺幅典型值為700mV,最小至最大窗口為500mV至900mV.要將LVDS的差分擺幅調整到600mV至1200mV的范圍,SiTime建議使用130Ω的端接電阻,如下圖3.0所示.它將典型的輸出擺幅值移至910mV,最小至最大范圍移至650mV至1170mV.為了使傳輸線和終端電阻完全匹配,建議將線阻抗增加到65Ω.

圖3.1.負載下的LVDS單AC端接

圖3.2.負載下的LVDS單AC端接

正在載入評論數據...

相關資訊

- [2019-09-21]LVDS差分晶振600mV至1200mV輸出...

- [2019-09-05]貼片諧振器負載容量適配器容量校...

- [2019-08-15]PETERMANN用于快速振蕩啟動的低...

- [2019-06-14]看晶振如何提供通信系統所需的信...

- [2019-04-28]憑借什么聲子晶體可以降低石英晶...

- [2019-04-03]KVG Crystal生產工藝簡要概述

- [2019-02-19]臺灣鴻星晶振的品質政策

業務經理

業務經理 客服經理

客服經理